1. O integriranih vezjih

1.1 Koncept in nastanek integriranih vezij

Integrirano vezje (IC): nanaša se na napravo, ki združuje aktivne naprave, kot so tranzistorji in diode, s pasivnimi komponentami, kot so upori in kondenzatorji, prek vrste specifičnih tehnik obdelave.

Vezje ali sistem, ki je "integriran" v rezino polprevodnika (kot je silicij ali spojine, kot je galijev arzenid) v skladu z določenimi medsebojnimi povezavami vezja in nato zapakiran v lupino za izvajanje določenih funkcij.

Leta 1958 je Jack Kilby, odgovoren za miniaturizacijo elektronske opreme pri Texas Instruments (TI), predlagal idejo o integriranih vezjih:

"Ker so vse komponente, kot so kondenzatorji, upori, tranzistorji itd., lahko izdelane iz enega materiala, sem pomislil, da bi jih bilo mogoče izdelati na kosu polprevodniškega materiala in jih nato povezati v celotno vezje."

12. septembra oziroma 19. septembra 1958 je Kilby dokončal izdelavo in predstavitev oscilatorja s faznim zamikom oziroma sprožilca, kar je označilo rojstvo integriranega vezja.

Leta 2000 je Kilby prejel Nobelovo nagrado za fiziko. Odbor za Nobelovo nagrado je nekoč komentiral, da je Kilby "postavil temelj sodobne informacijske tehnologije."

Spodnja slika prikazuje Kilbyja in njegov patent za integrirano vezje:

1.2 Razvoj tehnologije izdelave polprevodnikov

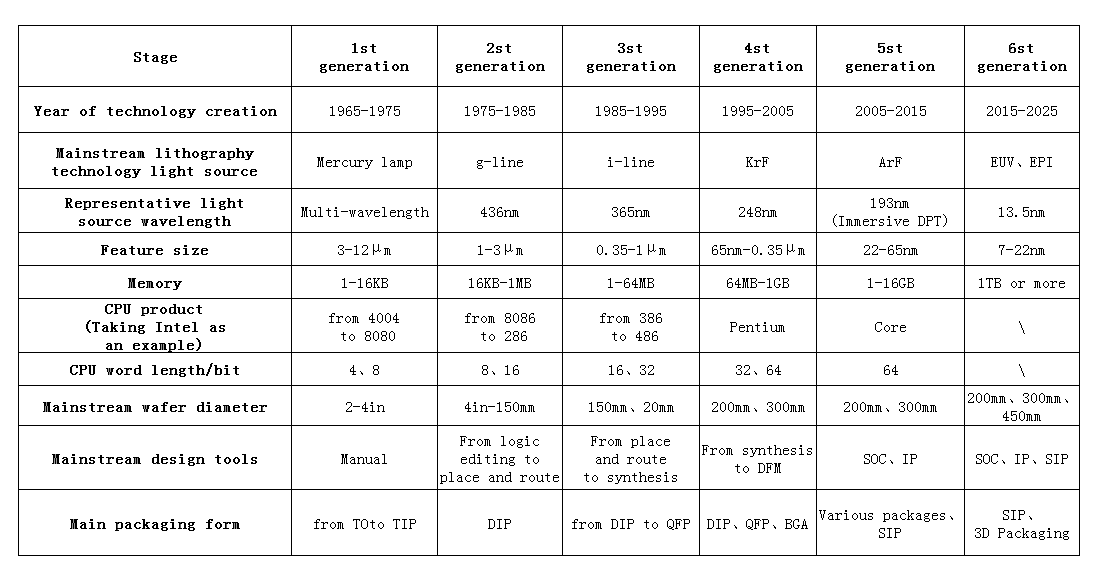

Naslednja slika prikazuje razvojne stopnje tehnologije izdelave polprevodnikov:

1.3 Industrijska veriga integriranih vezij

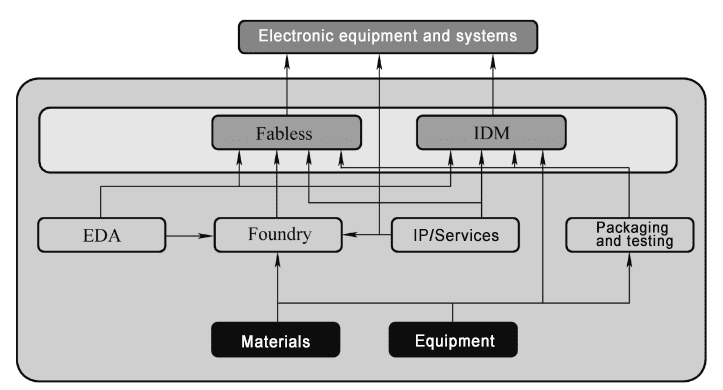

Sestava verige polprevodniške industrije (predvsem integrirana vezja, vključno z diskretnimi napravami) je prikazana na zgornji sliki:

- Fables: podjetje, ki oblikuje izdelke brez proizvodne linije.

- IDM: Integrated Device Manufacturer, proizvajalec integriranih naprav;

- IP: Proizvajalec modula vezja;

- EDA: Electronic Design Automatic, avtomatizacija elektronskega oblikovanja, podjetje ponuja predvsem orodja za oblikovanje;

- Livarna; Livarna rezin, nudenje storitev proizvodnje čipov;

- Pakiranje in testiranje livarskih podjetij: v glavnem služijo Fabless in IDM;

- Podjetja za materiale in posebno opremo: večinoma zagotavljajo potrebne materiale in opremo za podjetja za proizvodnjo čipov.

Glavni izdelki, proizvedeni s polprevodniško tehnologijo, so integrirana vezja in diskretne polprevodniške naprave.

Glavni izdelki integriranih vezij vključujejo:

- Standardni deli, specifični za aplikacijo (ASSP);

- mikroprocesorska enota (MPU);

- Spomin

- aplikacijsko specifično integrirano vezje (ASIC);

- Analogno vezje;

- Splošno logično vezje (Logical Circuit).

Glavni izdelki polprevodniških diskretnih naprav vključujejo:

- dioda;

- tranzistor;

- Napajalna naprava;

- visokonapetostna naprava;

- Mikrovalovna naprava;

- Optoelektronika;

- Senzorska naprava (Senzor).

2. Postopek izdelave integriranega vezja

2.1 Proizvodnja čipov

Na silicijevi rezini je mogoče hkrati izdelati več deset ali celo več deset tisoč specifičnih čipov. Število čipov na silicijevi rezini je odvisno od vrste izdelka in velikosti posameznega čipa.

Silicijeve rezine običajno imenujemo substrati. Premer silicijevih rezin se je z leti povečeval, od manj kot 1 palca na začetku do običajno uporabljenih 12 palcev (približno 300 mm) zdaj in je v prehodu na 14 ali 15 palcev.

Proizvodnja čipov je na splošno razdeljena na pet stopenj: priprava silicijeve rezine, proizvodnja silicijeve rezine, testiranje/izbiranje čipa, sestavljanje in pakiranje ter končno testiranje.

(1)

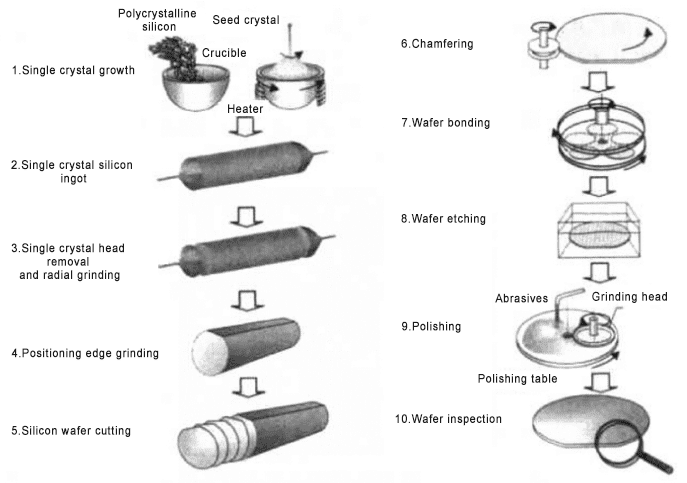

Priprava silicijeve rezine:

Za izdelavo surovine se silicij ekstrahira iz peska in prečisti. S posebnim postopkom nastanejo silicijevi ingoti ustreznega premera. Ingoti se nato razrežejo na tanke silicijeve rezine za izdelavo mikročipov.

Vaflji so pripravljeni v skladu s posebnimi specifikacijami, kot so zahteve za registrski rob in stopnje kontaminacije.

(2)Proizvodnja silicijevih rezin:

Gola silicijeva rezina, znana tudi kot proizvodnja čipov, prispe v obrat za proizvodnjo silicijevih rezin, nato pa gre skozi različne korake čiščenja, oblikovanja filma, fotolitografije, jedkanja in dopinga. Obdelana silicijeva rezina ima celoten nabor integriranih vezij, trajno vgraviranih na silicijevi rezini.

(3)Testiranje in izbor silicijevih rezin:

Po končani izdelavi silicijevih rezin se silicijeve rezine pošljejo v območje za testiranje/razvrščanje, kjer se posamezni čipi testirajo in električno testirajo. Nato se izločijo sprejemljivi in nesprejemljivi čipi, okvarjeni čipi pa se označijo.

(4)Montaža in pakiranje:

Po testiranju/razvrščanju rezin vstopijo rezine v korak sestavljanja in pakiranja, da se posamezni čipi zapakirajo v zaščitno cevno embalažo. Hrbtna stran rezine je brušena, da se zmanjša debelina podlage.

Na zadnjo stran vsake rezine je pritrjena debela plastična folija, nato pa se z žaginim rezilom z diamantno konico ločijo ostružki na vsaki rezini vzdolž rezalnih črt na sprednji strani.

Plastična folija na zadnji strani silicijeve rezine preprečuje, da bi silicijev čip odpadel. V montažnem obratu se dobri sekanci stisnejo ali izpraznijo, da nastane montažna embalaža. Kasneje se čip zapre v plastično ali keramično lupino.

(5)Končni test:

Da bi zagotovili funkcionalnost čipa, je vsako pakirano integrirano vezje preizkušeno, da izpolnjuje proizvajalčeve zahteve električnih in okoljskih značilnosti parametrov. Po končnem testiranju se čip pošlje kupcu v sestavo na za to namenjeni lokaciji.

2.2 Delitev procesa

Procesi izdelave integriranih vezij so na splošno razdeljeni na:

Front-end: Sprednji proces se na splošno nanaša na proizvodni proces naprav, kot so tranzistorji, ki v glavnem vključuje procese oblikovanja izolacije, strukture vrat, izvora in odtoka, kontaktnih lukenj itd.

Zadnji konec: Zaledni proces se v glavnem nanaša na oblikovanje medsebojnih povezovalnih linij, ki lahko prenašajo električne signale do različnih naprav na čipu, predvsem vključuje postopke, kot je nanašanje dielektrika med medsebojnimi povezovalnimi vodi, tvorjenje kovinskih linij in tvorjenje svinčenih blazinic.

Srednja faza: Da bi izboljšali delovanje tranzistorjev, napredna tehnološka vozlišča po 45 nm/28 nm uporabljajo dielektrike z vrati z visokim K in postopke kovinskih vrat ter dodajo postopke nadomestnih vrat in lokalne postopke medsebojnega povezovanja, potem ko sta izvorna in odvodna struktura tranzistorja pripravljena. Ti procesi so med front-end procesom in back-end procesom in se ne uporabljajo v tradicionalnih procesih, zato se imenujejo procesi na srednji stopnji.

Običajno je postopek priprave kontaktne luknje ločnica med začetnim in zadnjim postopkom.

Kontaktna luknja: luknja, vgravirana navpično v silicijevo rezino za povezavo kovinske medsebojne povezave prve plasti in naprave substrata. Napolnjena je s kovino, kot je volfram, in se uporablja za vodenje elektrode naprave do kovinske medsebojne povezovalne plasti.

Skozi luknjo: Je povezovalna pot med dvema sosednjima slojema kovinskih povezovalnih vodov, ki se nahaja v dielektrični plasti med dvema kovinskima slojema in je na splošno napolnjena s kovinami, kot je baker.

V širšem smislu:

Front-end proces: V širšem smislu bi morala proizvodnja integriranih vezij vključevati tudi testiranje, pakiranje in druge korake. V primerjavi s testiranjem in pakiranjem je proizvodnja komponent in medsebojnih povezav prvi del proizvodnje integriranih vezij, ki se skupaj imenujejo front-end procesi;

Zaledni proces: Testiranje in pakiranje imenujemo zaledni procesi.

3. Dodatek

SMIF: standardni mehanski vmesnik

AMHS: avtomatiziran sistem za predajo materiala

OHT: Prenos z nadzemnim dvigalom

FOUP: enoten pod s sprednjim odpiranjem, ekskluzivno za 12-palčne (300 mm) rezine

Še pomembneje,Semicera lahko zagotovigrafitnih delov, mehka/trda klobučevina,deli iz silicijevega karbida, CVD deli iz silicijevega karbida, inDeli, prevlečeni s SiC/TaCs polnim polprevodniškim postopkom v 30 dneh.Iskreno se veselimo, da bomo postali vaš dolgoročni partner na Kitajskem.

Čas objave: 15. avgusta 2024